# Configurable Logic: A Dynamically Programmable Cellular Architecture and its VLSI Implementation.

Thomas Andrew Kean

Ph D

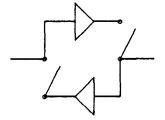

University of Edinburgh

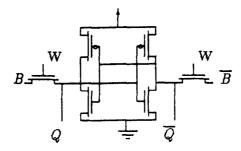

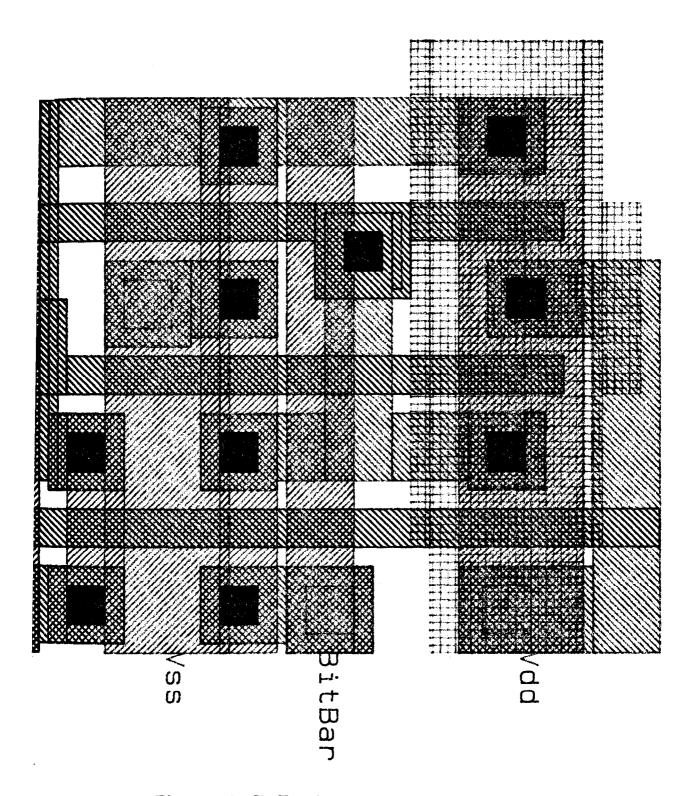

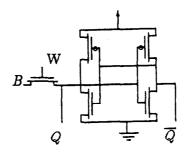

1988

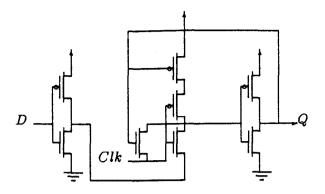

I declare that that this thesis has been composed by myself and that the work reported within is entirely my own except where clearly indicated otherwise in the text.

Thomas Kean.

9. 16on.

Copyright ©1988 Thomas Kean All rights reserved.

#### Abstract

At present there are two main paradigms for computation: interpretation of a data stream representing a program by a processing unit (software) and an interconnection of active logic elements (hardware). While both systems can (given reasonable definitions) be shown to be equivalent in terms of which functions they can compute they have radically different properties: hardware can potentially provide a much higher performance implementation of a single simple algorithm whereas software can implement a wide variety of extremely complex algorithms. Here we will consider a third paradigm for computation - configurable hardware - in which the interconnection between the active logic elements is dependant on a control store. This paradigm can potentially offer many of the performance advantages of hardware while retaining much of the flexibility of software.

This thesis examines the general properties of configurable systems and examples of previous designs in order to develop a new cellular-array architecture called Configurable Array Logic (CAL). The implementation of this architecture a related statically-programmed system, the Configurable Logic Array (CLA) in VLSI are discussed. The potential of the CAL system for implementation using Wafer Scale Integration is considered. The CAD system which would be required to allow algorithms expressed in normal programming languages to be implemented on the cellular architecture is discussed and the tools developed during the course of the project are covered. Four example designs using the system are presented: a digital stopwatch, a Data Encryption Standard (DES) encryptor, a unit to compute the 3-4 distance transform (which is used in image pattern matching) and a sketch of a system using configurable logic to implement cellular-automaton models for fluid-flow simulations. Finally, methods of extending the Configurable Logic architecture to allow more complex computations to be performed and other directions for further research are discussed.

| Intr | oducti            | on.                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Softwa            | re                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.2  | Hardw             | are                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.3  | Config            | urable Hardware                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 1.3.1             | EPLD Replacement                                                                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 1.3.2             | Prototype System for ASIC's                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 1.3.3             | Algorithm Machine                                                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4  | Overv             | iew of Thesis                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Prin | nciples           | of Configurable Systems.                                                                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1  | Circui            | t Model                                                                                                                             | 13                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.1.1             | Definition of Circuit                                                                                                               | 14                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.1.2             | Definition of Configurable Circuit                                                                                                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.1.3             | Definition of c-CLM                                                                                                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.1.4             | Lower Bounds                                                                                                                        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.1.5             | Circuits and Functions                                                                                                              | 19                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2  | Efficie           | ncy                                                                                                                                 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.2.1             | Efficiency of Configurable Circuits                                                                                                 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.2.2             | Functional Efficiency                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 1.1<br>1.2<br>1.3 | 1.1 Softwa 1.2 Hardw 1.3 Config 1.3.1 1.3.2 1.3.3 1.4 Overvi  Principles 2.1 Circui 2.1.1 2.1.2 2.1.3 2.1.4 2.1.5 2.2 Efficie 2.2.1 | 1.2 Hardware.  1.3 Configurable Hardware.  1.3.1 EPLD Replacement.  1.3.2 Prototype System for ASIC's.  1.3.3 Algorithm Machine.  1.4 Overview of Thesis.  Principles of Configurable Systems.  2.1 Circuit Model.  2.1.1 Definition of Circuit.  2.1.2 Definition of Configurable Circuit.  2.1.3 Definition of c-CLM.  2.1.4 Lower Bounds.  2.1.5 Circuits and Functions.  2.2 Efficiency.  2.2.1 Efficiency of Configurable Circuits. |

|    |      | 2.2.3     | Utilisation                          | 23         |

|----|------|-----------|--------------------------------------|------------|

|    | 2.3  | Design    | Goals                                | 24         |

|    |      | 2.3.1     | Device Structure                     | 27         |

|    |      | 2.3.2     | Utilisation and Cell Generality.     | 28         |

|    |      | 2.3.3     | Costs and Benefits                   | 32         |

|    | 2.4  | Timing    | g Discipline.                        | 33         |

|    |      | 2.4.1     | Self-Timed                           | 33         |

|    |      | 2.4.2     | Clocked                              | 33         |

|    |      | 2.4.3     | Pipelined                            | 34         |

|    |      | 2.4.4     | Unsynchronised                       | 34         |

|    | 2.5  | Summa     | ary                                  | 34         |

| 2  | Des  | ian of    | Configurable Systems.                | 35         |

| J. | Des. | ign or    | Configurable Systems.                | ,,         |

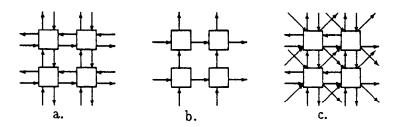

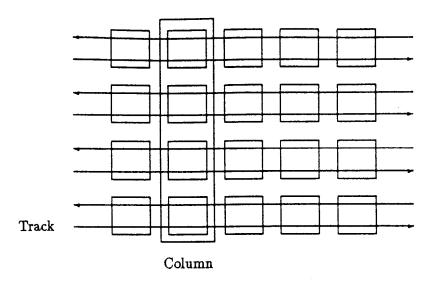

|    | 3.1  | Conne     | ctivity Between Cells                | 36         |

|    |      | 3.1.1     | Nearest Neighbour Connections        | 38         |

|    |      | 3.1.2     | Nearest Neighbour with Longer Busses | 38         |

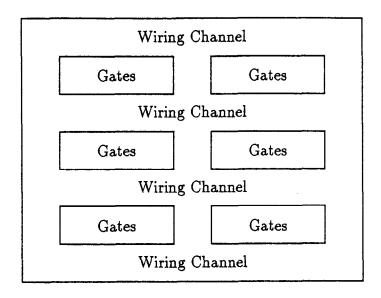

|    |      | 3.1.3     | Wiring Channels                      | 40         |

|    | 3.2  | Functi    | on Unit Design                       | <b>4</b> 5 |

|    |      | 3.2.1     | Combinational Complexity.            | 45         |

|    |      | 3.2.2     | Common Approaches                    | 47         |

|    |      | 3.2.3     | Number of Function Units             | 48         |

|    |      | 3.2.4     | Number Of Inputs                     | <b>4</b> 9 |

|    |      | 3.2.5     | Implementing Function Units          | <b>1</b> 9 |

|    |      | 3.2.6     | Sequential Function                  | 50         |

|    | 2 2  | Within    | Cell Routing                         | 52         |

|    | U    | ** ****** |                                      | ,,         |

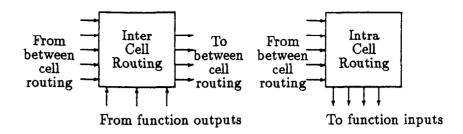

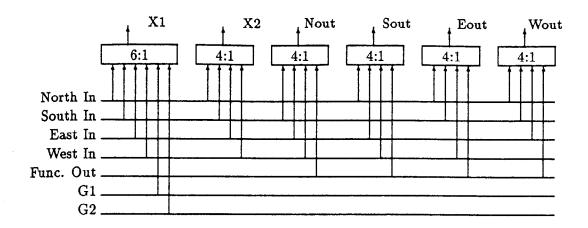

|            |     | 3.3.1  | Inter-Cell Routing                 |

|------------|-----|--------|------------------------------------|

|            |     | 3.3.2  | Intra-Cell Routing                 |

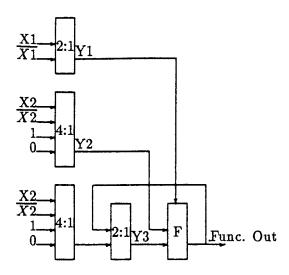

|            | 3.4 | Config | urable Logic Design                |

|            |     | 3.4.1  | Between Cell Communication         |

|            |     | 3.4.2  | Within-Cell Communication          |

|            |     | 3.4.3  | Function                           |

|            |     | 3.4.4  | Improvements                       |

|            | 3.5 | Comp   | arison with Previous Designs       |

|            |     | 3.5.1  | Two Level Designs                  |

|            |     | 3.5.2  | Generalised PLA Architectures      |

|            |     | 3.5.3  | Minnick's Cutpoint Cell            |

|            |     | 3.5.4  | Shoup's Control Array Cell         |

|            |     | 3.5.5  | The Xilinx Programmable Gate Array |

|            |     | 3.5.6  | The Actel ACT Series               |

|            | 3.6 | Summ   | ary                                |

| <b>1</b> . | VLS | SI Imp | lementation. 86                    |

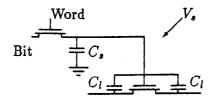

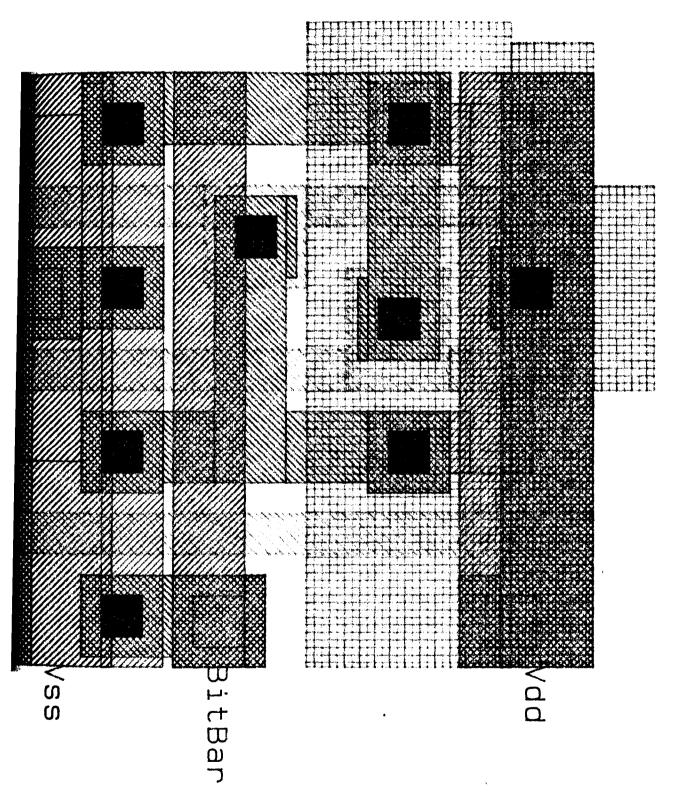

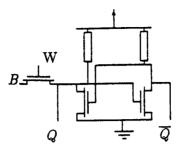

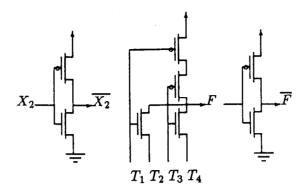

|            | 4.1 | Imple  | mentation of Control Store         |

|            | 4.2 | RAM    | Control Stores                     |

|            |     | 4.2.1  | Dynamic Designs                    |

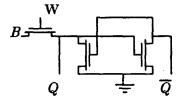

|            |     | 4.2.2  | Static Designs                     |

|            |     | 4.2.3  | Candidate Designs                  |

|            |     | 4.2.4  | Design Choice                      |

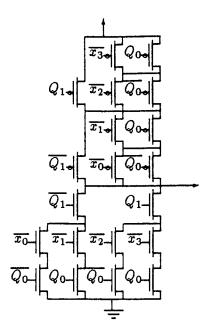

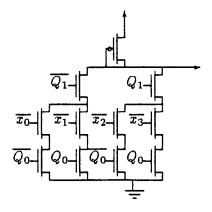

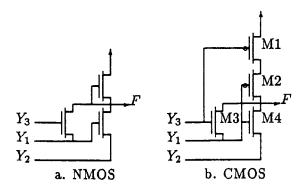

|            | 4.3 | Multip | olexor Design                      |

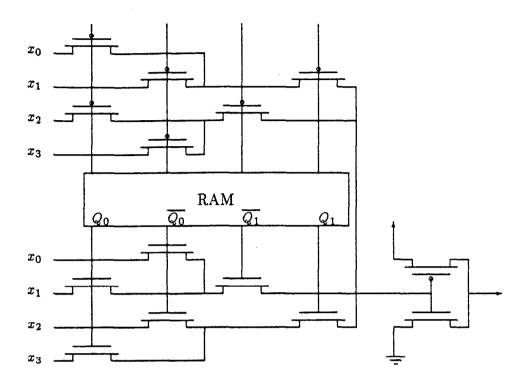

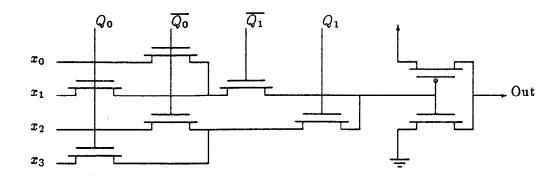

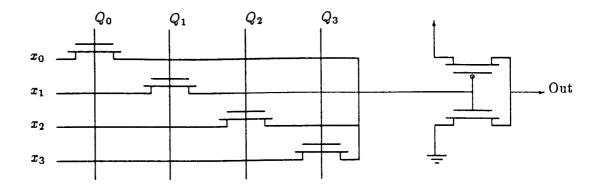

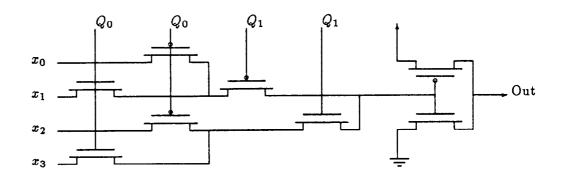

|            |     | 4.3.1  | Candidate Designs                  |

|    |     | 4.3.2  | Performance             | •  |       |     | •   |        | <br>• | • |   | • | • | • | . 1 | 10  |

|----|-----|--------|-------------------------|----|-------|-----|-----|--------|-------|---|---|---|---|---|-----|-----|

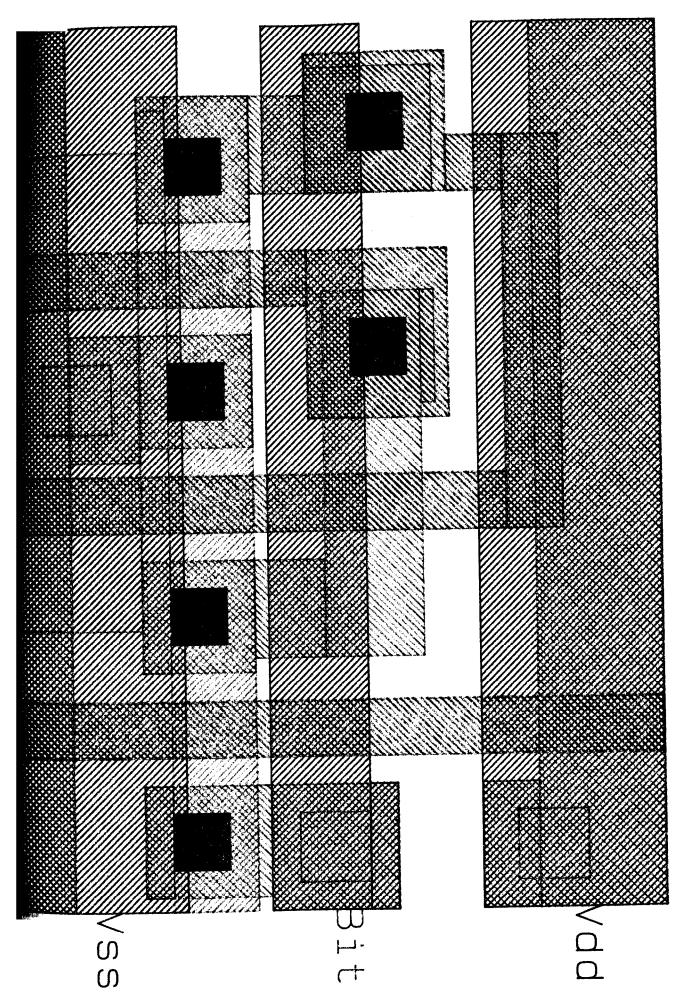

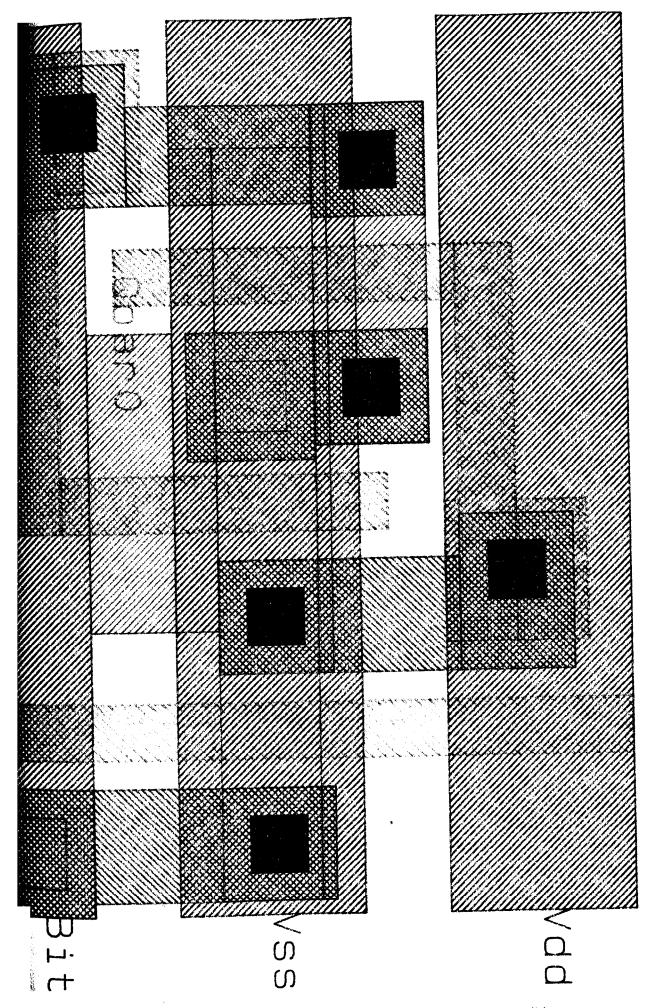

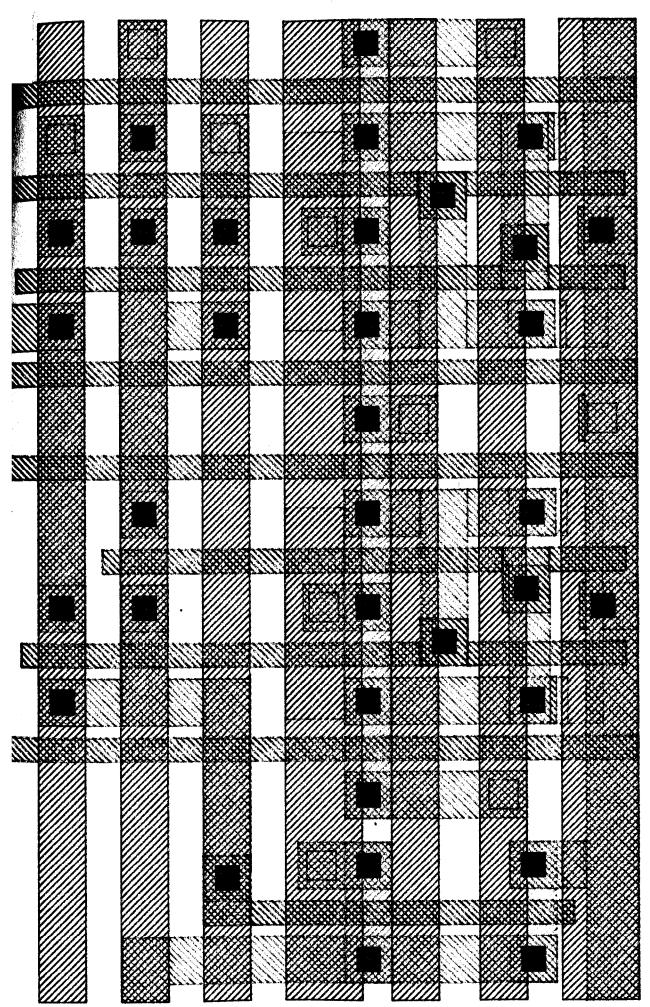

|    | 4.4 | Cell D | esign                   | •  | <br>• |     |     |        |       |   |   |   | • | • | . 1 | 12  |

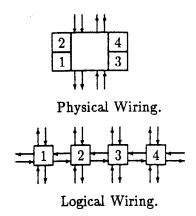

|    |     | 4.4.1  | Aspect Ratio            | •  |       |     |     |        |       |   |   |   |   | • | . 1 | 14  |

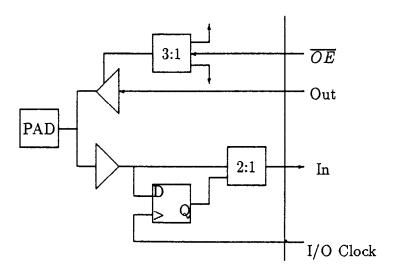

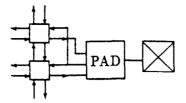

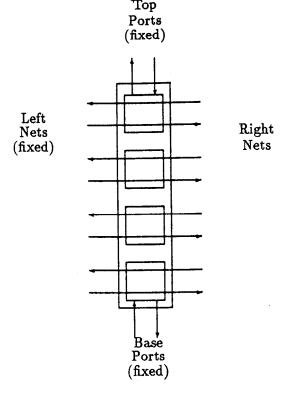

|    | 4.5 | Input  | Output Blocks           | •  |       |     |     |        |       |   |   |   |   |   | . 1 | .15 |

|    |     | 4.5.1  | The CAL EPLD Approach   | ١. |       |     |     |        | <br>• |   |   |   |   | • | . 1 | .16 |

|    |     | 4.5.2  | The CAL Array Approach. |    |       |     |     |        |       |   |   | • |   |   | . 1 | .17 |

|    | 4.6 | Progra | mming                   |    | <br>• |     |     |        |       |   |   |   | • | • | . ] | .19 |

|    |     | 4.6.1  | External Interface      |    |       | • • |     | <br>•  | <br>• |   |   |   |   |   | . 1 | 19  |

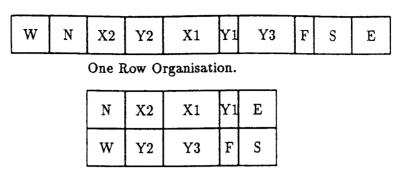

|    |     | 4.6.2  | Internal Design         |    |       |     |     | <br>•  | <br>• |   |   |   |   |   | . 1 | 20  |

|    |     | 4.6.3  | Possible Improvements   |    | <br>• |     | •   | <br>•  |       | • |   |   |   |   | . 1 | 23  |

|    | 4.7 | Global | Signals                 |    |       |     | •   |        |       | • |   |   |   |   | . ] | 24  |

|    |     | 4.7.1  | G1 and G2               |    |       |     |     |        |       | • |   |   |   | • | . 1 | 24  |

|    |     | 4.7.2  | Ftest                   | •  | <br>• |     |     | <br>•  |       |   |   |   | • |   | . 1 | 24  |

|    | 4.8 | Power  | Supply Distribution     |    | <br>• |     | •   |        | <br>• |   |   |   |   | • | . 1 | 25  |

|    |     | 4.8.1  | Array Requirements      |    |       |     | •   | <br>•  |       |   |   |   |   |   | . 1 | 125 |

|    |     | 4.8.2  | Pad Requirements        |    | <br>• |     |     |        |       | • |   |   |   | • | . 1 | 127 |

|    | 4.9 | Summ   | ary                     |    |       |     | •   | <br>•  |       | • |   |   |   |   | . 1 | 28  |

| 5  | Sno | oifa V | LSI Implementations.    |    |       |     |     |        |       |   |   |   |   |   | 7   | 29  |

| υ. | Spe |        | •                       |    |       |     |     |        |       |   |   |   |   |   |     |     |

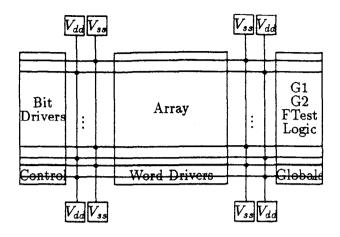

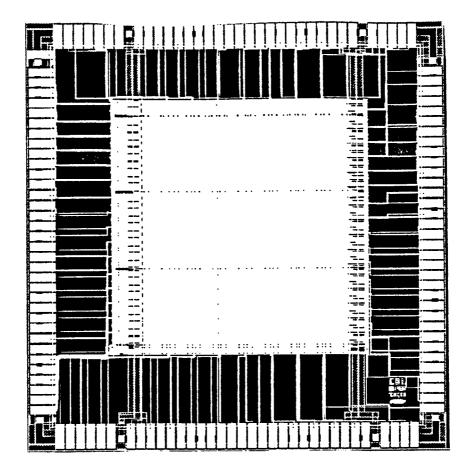

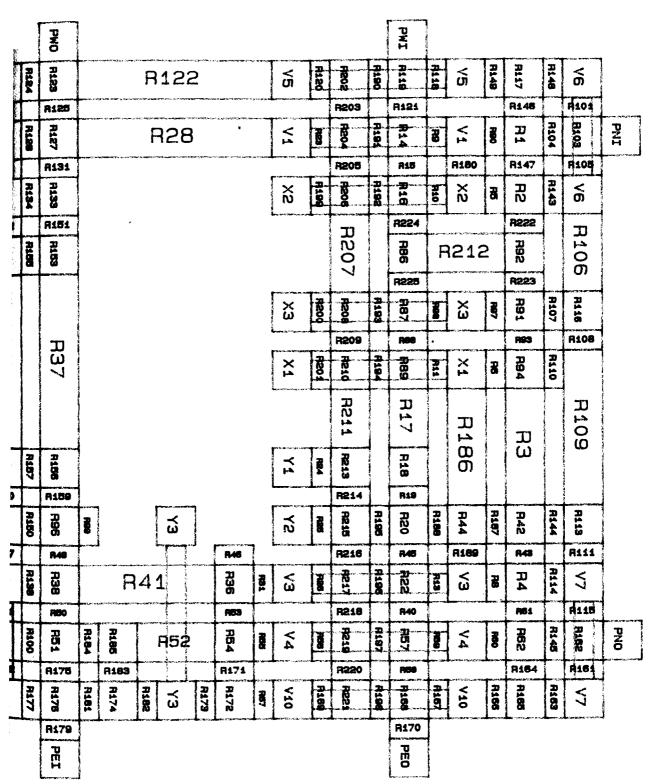

|    | 5.1 | The C  | AL Chip                 | •  | <br>• |     | , • | <br>•  | <br>• | • | • | • | • |   | . 1 | 30  |

|    |     | 5.1.1  | History                 | •  | <br>• |     | •   | <br>•  | <br>٠ |   |   |   |   |   | . 1 | 30  |

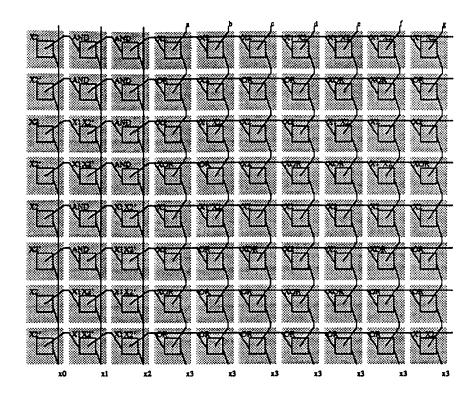

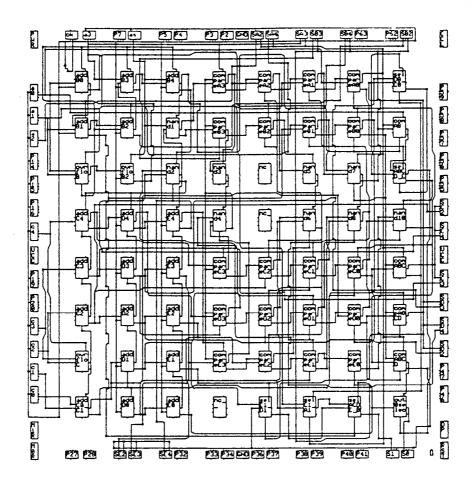

|    |     | 5.1.2  | Chip Design             | ٠. |       |     | •   | <br>•. | <br>• | • |   |   |   |   | . 1 | 30  |

|    |     | 5.1.3  | Design Validation       | •  |       |     | •   | <br>•  |       |   |   |   |   |   | . 1 | 32  |

|    |     | 5.1.4  | Testing the CAL         | •  | <br>• |     | •   | <br>•  | <br>• | • | • |   |   |   | . 1 | 35  |

|    |     | 5.1.5  | Fault Tolerance         |    |       |     |     |        |       |   |   |   |   |   | . 1 | 37  |

| 5.2 | CLA I      | mplementation                                                                                                                                             |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 5.2.1      | Basic Design                                                                                                                                              |

|     | 5.2.2      | Final Design                                                                                                                                              |

|     | 5.2.3      | Scan Path Cell                                                                                                                                            |

|     | 5.2.4      | CLA Personalisation                                                                                                                                       |

|     | 5.2.5      | Useful Techniques                                                                                                                                         |

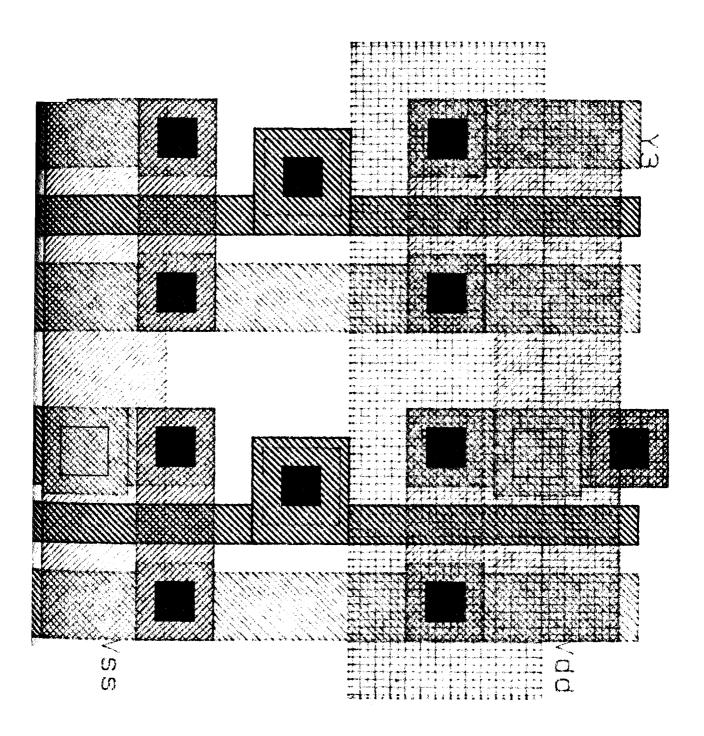

| 5.3 | Wafer      | Scale Version                                                                                                                                             |

|     | 5.3.1      | Design Overview                                                                                                                                           |

|     | 5.3.2      | Reconfiguration Methods                                                                                                                                   |

|     | 5.3.3      | Implementation of Reconfiguration System                                                                                                                  |

|     | 5.3.4      | Normal Processing                                                                                                                                         |

|     | 5.3.5      | Special Processing                                                                                                                                        |

|     | 5.3.6      | Technology Choice                                                                                                                                         |

| 5.4 | Summ       | ary                                                                                                                                                       |

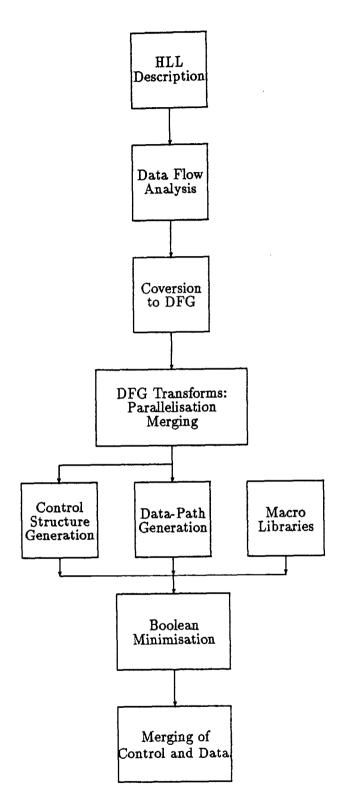

| CA  | D Tool     | s for Configurable Logic. 165                                                                                                                             |

| 6.1 | Applic     | ations of Configurable Logic                                                                                                                              |

|     | 6.1.1      | EPLD Replacement                                                                                                                                          |

|     | 6.1.2      | ASIC Prototyping                                                                                                                                          |

|     | 6.1.3      | Algorithm Implementation                                                                                                                                  |

| 6.2 | Active     | Compilation                                                                                                                                               |

|     | 6.2.1      | Source Language                                                                                                                                           |

|     | 6.2.2      | Choice of Code Segments                                                                                                                                   |

|     | 6.2.3      | Synthesis Operations                                                                                                                                      |

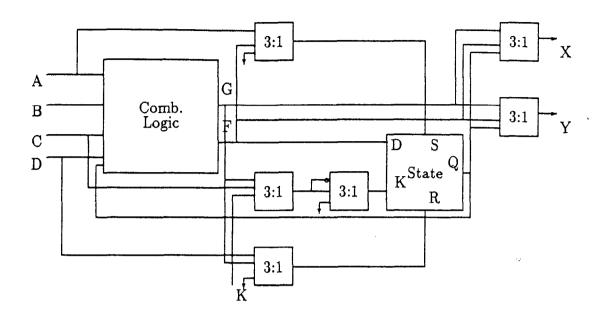

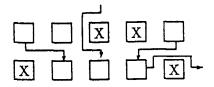

|     | 6.2.4      | Control Structure Realisation                                                                                                                             |

|     | 5.4<br>CA1 | 5.2.1 5.2.2 5.2.3 5.2.4 5.2.5 5.3 Wafer 5.3.1 5.3.2 5.3.3 5.3.4 5.3.5 5.3.6 5.4 Summ  CAD Tool 6.1 Applied 6.1.1 6.1.2 6.1.3 6.2 Active 6.2.1 6.2.2 6.2.3 |

|      | 6.2.5  | Cell Assembly                        | 78  |

|------|--------|--------------------------------------|-----|

| 6.3  | Data-S | Structures for Describing CAL        | 81  |

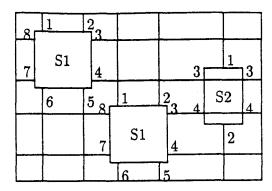

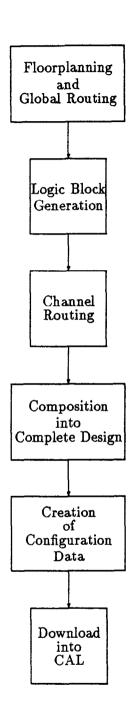

| 6.4  | Floorp | planning and Global Routing          | 86  |

| 6.5  | Logic  | Synthesis Methods                    | 87  |

|      | 6.5.1  | Cascades                             | 88  |

|      | 6.5.2  | Trees                                | 88  |

|      | 6.5.3  | Tandem Nets                          | 89  |

|      | 6.5.4  | Irregular Structures                 | 89  |

|      | 6.5.5  | Summary                              | 90  |

|      | 6.5.6  | Binary Decision Trees                | 90  |

| 6.6  | The L  | ogic Synthesis Program               | 91  |

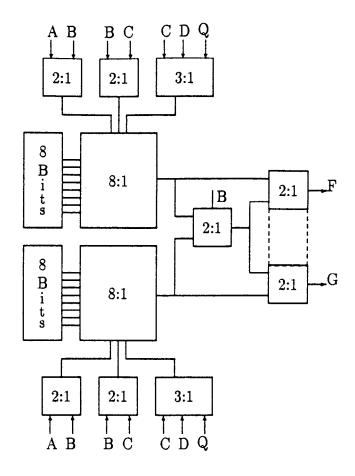

|      | 6.6.1  | The Configurable Logic ROM Generator | 95  |

| 6.7  | Struct | ural Layout                          | 98  |

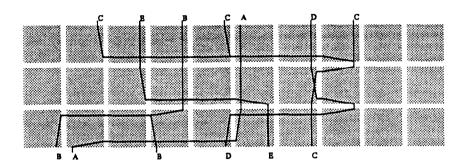

| 6.8  | Routin | ng                                   | 99  |

|      | 6.8.1  | Channel Routing                      | 99  |

|      | 6.8.2  | Maze Routing                         | 03  |

| 6.9  | Graph  | nical Tools                          | 04  |

|      | 6.9.1  | The Leaf Cell Editor                 | 04  |

| 6.10 | Optim  | nisation                             | 05  |

| 6.11 | Back 1 | End Tools                            | 07  |

|      | 6.11.1 | MODEL Interface                      | :07 |

|      | 6.11.2 | CIF generation                       | 07  |

|      | 6.11.3 | CAL Programming                      | :09 |

| 6 19 | Summ   | nary                                 | 'nC |

| <b>7</b> . | Des | ign Ex          | amples.                            |      |      | 211   |

|------------|-----|-----------------|------------------------------------|------|------|-------|

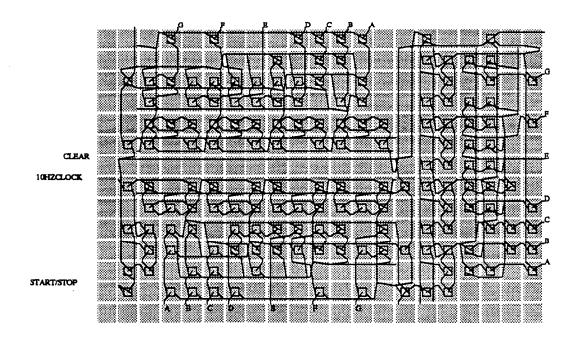

|            | 7.1 | Stopwa          | atch Example                       | <br> | <br> | . 211 |

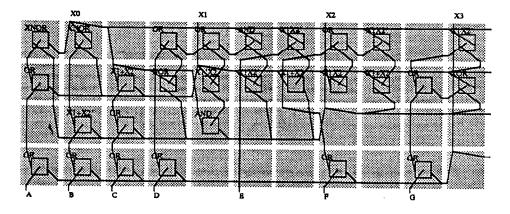

|            |     | 7.1.1           | The Counter                        | <br> | <br> | . 212 |

|            |     | 7.1.2           | The Decoder                        | <br> | <br> | . 213 |

|            |     | 7.1.3           | The Control Logic.                 | <br> | <br> | . 216 |

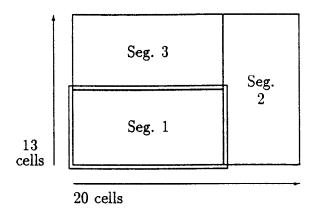

|            |     | 7.1.4           | Floorplan                          | <br> | <br> | . 216 |

|            |     | 7.1.5           | CLA Implementation                 | <br> | <br> | . 216 |

|            |     | 7.1.6           | Size Comparisons                   | <br> | <br> | . 219 |

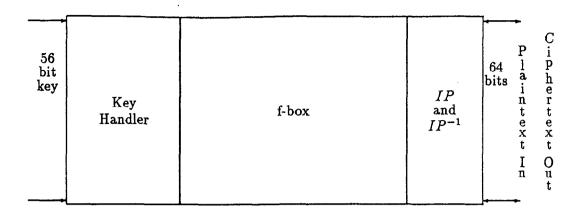

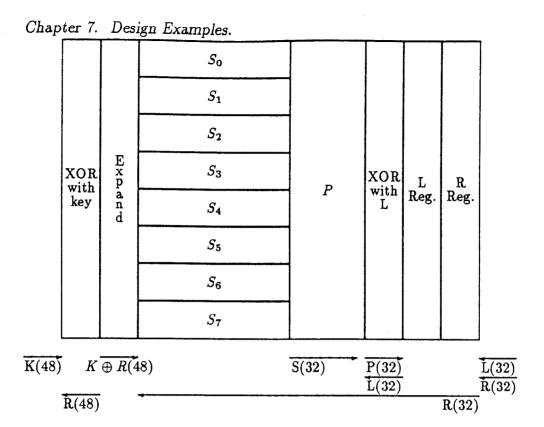

|            | 7.2 | Data 1          | Encryption Standard Example        | <br> | <br> | . 220 |

|            |     | 7.2.1           | Introduction to DES                | <br> | <br> | . 220 |

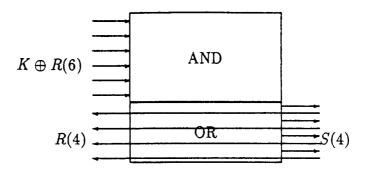

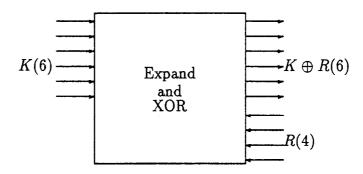

|            |     | 7.2.2           | The DES process                    | <br> | <br> | . 221 |

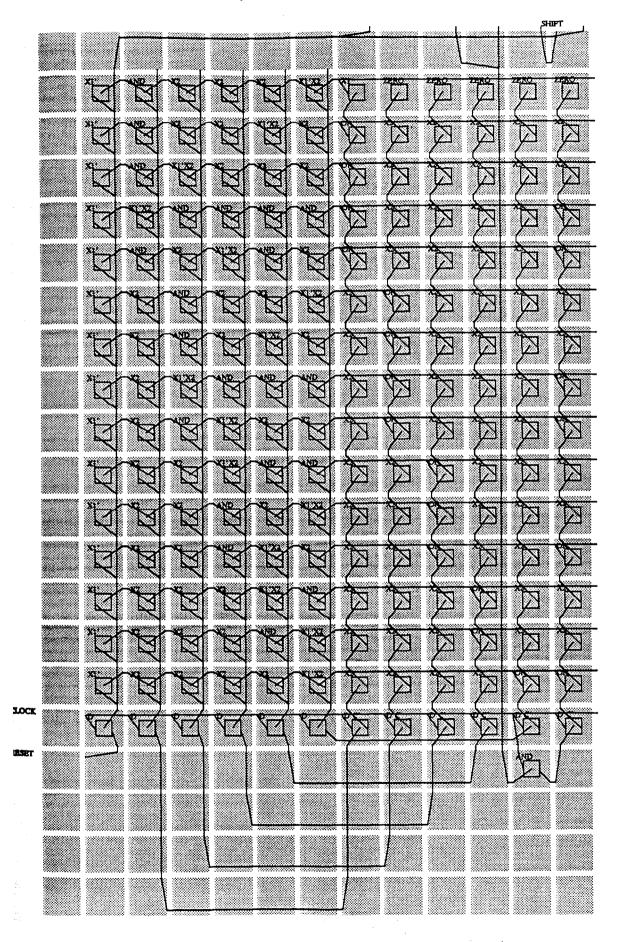

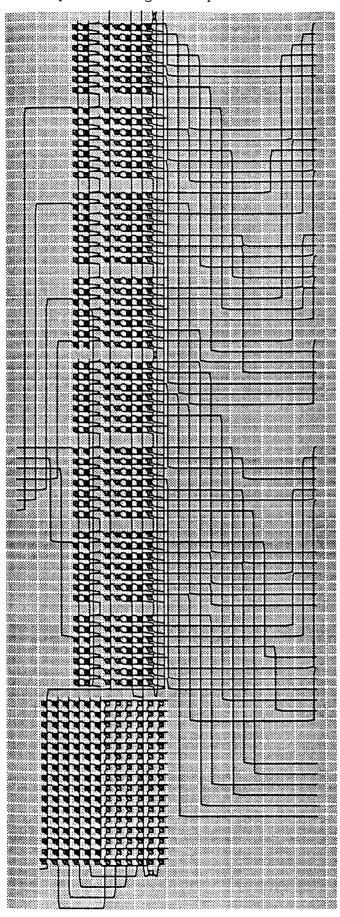

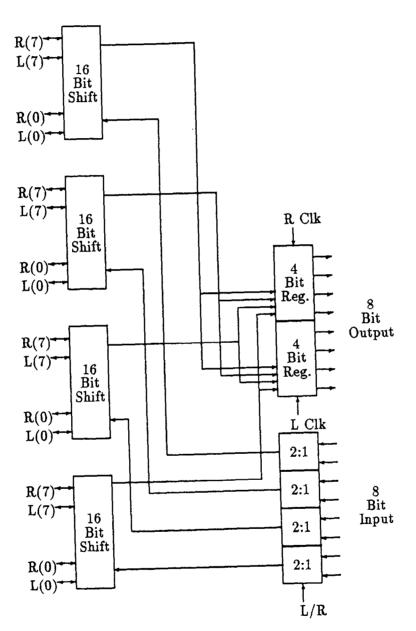

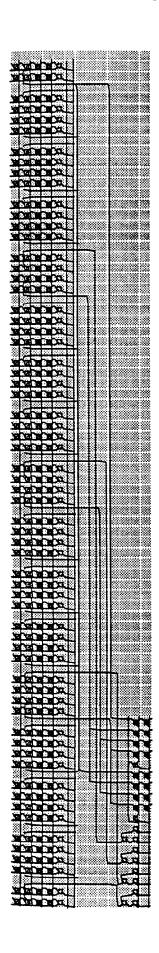

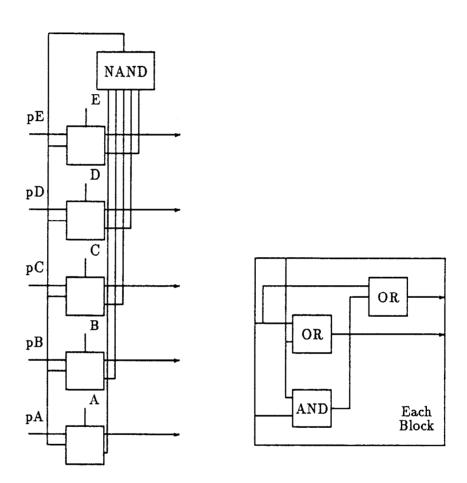

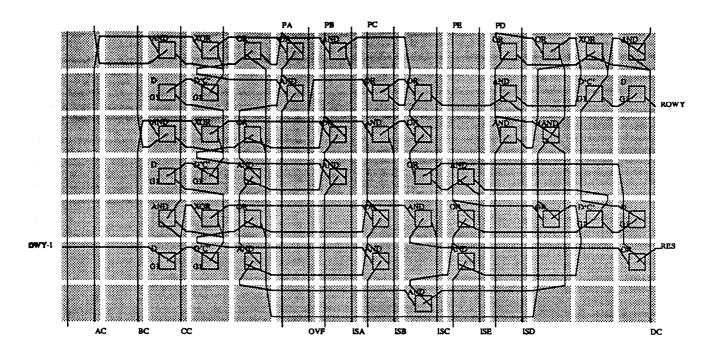

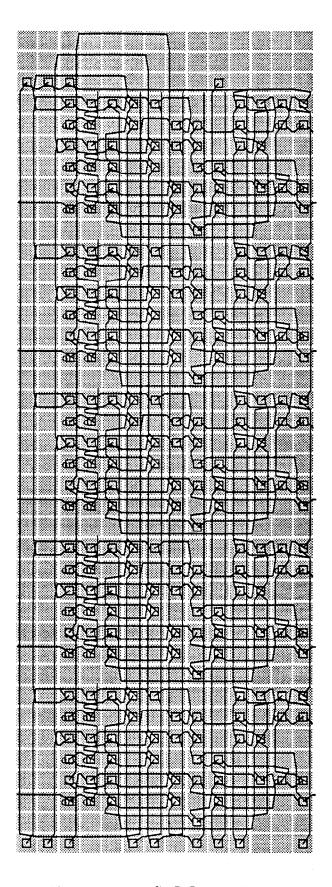

|            |     | 7.2.3           | Implementation of DES              | <br> | <br> | . 226 |

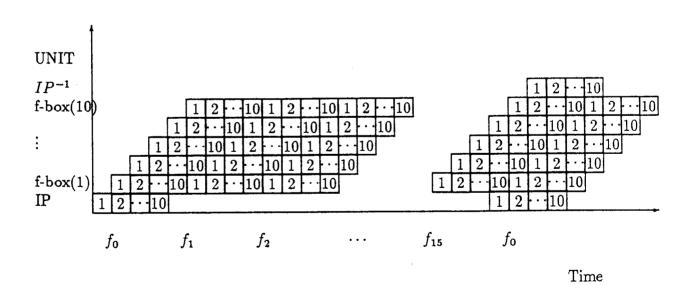

|            |     | 7.2.4           | Pipelining                         | <br> | <br> | . 238 |

|            |     | 7.2.5           | Performance                        | <br> | <br> | . 241 |

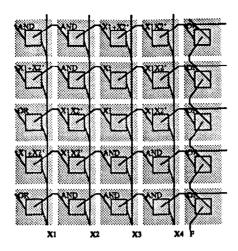

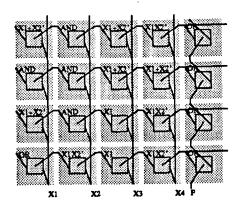

|            | 7.3 | Image           | e Processing                       | <br> | <br> | . 242 |

|            |     | 7.3.1           | The Sample Problem                 | <br> | <br> | . 243 |

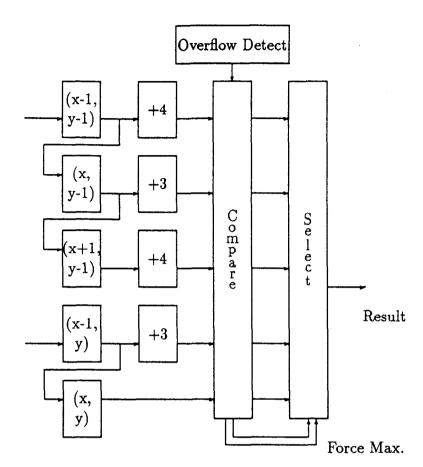

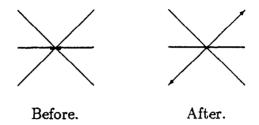

|            |     | 7.3.2           | The Distance Transform Calculation | <br> | <br> | . 244 |

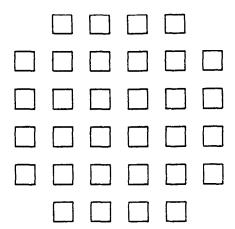

|            |     | 7.3.3           | LCA Implementation                 | <br> | <br> | . 247 |

|            |     | 7.3.4           | CAL Implementation.                | <br> | <br> | . 247 |

|            |     | 7.3.5           | Implementation Comparisons         | <br> | <br> | . 250 |

|            |     | 7.3.6           | Conclusions                        | <br> | <br> | . 254 |

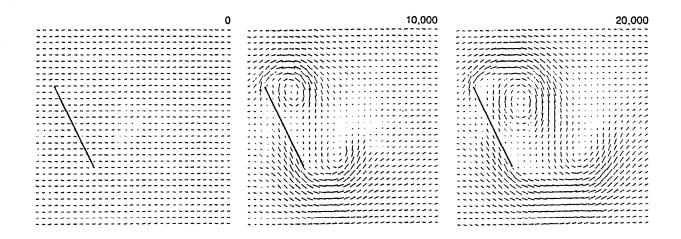

|            | 7.4 | Fluid           | Flow Simulation                    | <br> | <br> | . 254 |

|            |     | 7.4.1           | The Model                          | <br> | <br> | . 255 |

|            |     | $\tilde{7}.4.2$ | Architecture                       | <br> | <br> | . 257 |

|    |     | 7.4.3  | Comparison with Previous Systems |   |

|----|-----|--------|----------------------------------|---|

|    |     | 7.4.4  | Conclusions                      | ; |

|    | 7.5 | Summ   | ary                              | į |

| 8. | Con | clusio | ns and Future Work. 265          | ; |

|    | 8.1 | Overvi | ew of Thesis                     |   |

|    | 8.2 | Develo | pment                            | • |

|    |     | 8.2.1  | Idealised Silicon                | • |

|    |     | 8.2.2  | Other Architectures              | ; |

|    | 8.3 | Virtua | l Cells                          | , |

|    |     | 8.3.1  | Overlays                         | , |

|    |     | 8.3.2  | Paging                           | ) |

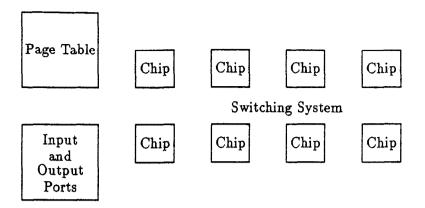

|    |     | 8.3.3  | Switching System                 | ) |

|    |     | 8.3.4  | Extra Cell Hardware              |   |

|    |     | 8.3.5  | Conclusions                      | • |

|    | 8.4 | Conclu | asions                           |   |

|    | 8.5 | Ackno  | wledgments                       |   |

# Chapter 1

# Introduction.

At present there are two main methods of implementing algorithms: interpretation of a data stream representing a program by an active processing unit (software) and interconnection of active logic elements (hardware). In one case the computation performed is dependant on data stored in memory and in the other on the interconnection between a set of physical devices (transistors). Both paradigms can be shown (given reasonable definitions) to be essentially equivalent in terms of the functions they can compute (see, for example, [Savage76]). In this chapter we will examine the strengths and weaknesses of these paradigms and make the case for a third paradigm: Configurable Hardware in which the interconnection between active logic elements (and hence the function computed) is dependant on a control store.

#### 1.1 Software.

The traditional computer architecture consists of a complex processor connected to a very large memory containing both program code and data. This architecture is extremely powerful and has allowed the development of today's complex information processing systems. The use of a single processor, however, results in a fundamental limitation on the performance of such computer systems since there are physical (light-speed) limitations on the speed of individual components. These

limitations are starting to be approached by current technologies and 'parallel' architectures with multiple processors which avoid this bottleneck by performing many operations at the same time are becoming important.

Let us consider the potential performance of a software implementation of an algorithm versus a hardware one: we can see many areas in which the hardware implementation is guaranteed to be faster and more efficient.

- 1. Instruction Fetch/Decode. In a hardware system the function is fixed so no time or area is wasted storing, fetching or decoding instructions.

- 2. Word Length. In a hardware implementation operations on single bits can use bit wide units and operations on 64 bit words 64 bit wide units: in software both operations would probably use 32 bit wide units resulting in an area penalty in the first case and a time penalty in the second.

- 3. Calculation Efficiency. In a hardware implementation calculations can be done using tailored hardware units which use the most efficient possible gate level implementation of a function: in software computations must use a series of predefined instructions. For example, a five way comparator could be implemented as a single hardware unit whereas a software system would usually need to use 4 two way comparison operations. Similarly, a general purpose software processor will often have a large amount of hardware to support instructions not required by the current computation (e.g. floating point units in a text processing application).

- 4. Memory Size. General purpose computers must provide memory systems large enough to support the algorithm with the worst case memory requirements: thus most algorithms will not make full use of the available memory. Hardware systems, on the other hand, can provide exactly the memory required by the current algorithm.

All of these problems are readily surmountable in a single processor system where it is economic to provide the extra resources: they are much more significant

in a parallel computer system where as well as providing as much memory and computation as possible in each processor node one also wishes to provide as many nodes as possible. There does not seem to be any reasonable way of getting round this problem and all current systems which provide a large number of conventional processing nodes are in the supercomputer price range.

#### 1.2 Hardware.

In recent years many hardware implementations of important algorithms have been suggested (see, for example, the bibliography in [Wolfram86]). These take advantage of the factors mentioned above to provide huge speedups over conventional serial and parallel computers. Direct hardware implementation of realistic algorithms has only become feasible with the advent of Very Large Scale Integrated (VLSI) circuit technology and the recent advances in CAD tools which have made possible the Application Specific Integrated Circuit (ASIC). In this section, therefore, we will consider hardware as being synonomous with VLSI circuits.

Despite the enormous performance advantages of hardware over software these systems are not without problems.

- ASIC's are hard to design well. To get maximum utilisation of the silicon area available a detailed knowledge of VLSI design techniques is required. Array structures designed at the mask level can sometimes provide huge savings.

- 2. ASIC's are expensive to build. ASIC's are very expensive in low volumes because of the high capital cost of processing equipment and the relatively large per-design cost caused by different handling requirements and mask-making. Even when direct-write electron-beam machines are used to eliminate mask-making large amounts of computer time are required to determine patterning information and the expensive electron-beam machine is tied up for a considerable time on each chip. This makes prototyping ASIC's costly.

- 3. ASIC's designs are hard to verify. The complexity of ASIC designs means that a huge amount of CPU time is necessary to simulate them at gate or transistor level on a serial computer. Catalogue part designs are usually prototyped rather than simulated at low level. Simulation times on conventional computers cannot be expected to improve with technology since, in general, the technology being used to develop a new ASIC (and hence its complexity) will be ahead of the technology used in the computer it is simulated on.

- 4. ASIC's are hard to test. When designing with catalogue parts the engineer expects the manufacturer to test the parts before they are shipped: he can assume that the parts he uses are all good. In most cases the problem of testing for chip production faults can be ignored.

Every new ASIC design, on the other hand, must have a set of test vectors determined for it: this usually involves fault simulation to test that a particular set of test vectors exercises all internal nodes in the design. Determination of appropriate test vectors requires detailed knowledge of the design and so it must be done by the systems engineer: this is an additional and time consuming task. Automatic test pattern generation programs coupled with a suitable design methodology can ease this problem but they are not a complete solution. Such programs work with gate-level descriptions rather than mask level ones and so must still be used by the system designer. Efficient automatic test pattern generation is only possible for certain classes of sub-components, notably combinational logic blocks, the systems engineer must integrate automatically generated and manually generated patterns for subcomponents into a test set for the whole design.

5. ASIC's are hard to change. ASIC designs are hard to change because every change, however slight, involves redoing the verification steps, determining a new set of test vectors and producing a new design for fabrication. Incremental design systems could reduce the verification and test pattern generation overhead but there is a strong motivation to rerun these steps completely to make absolutely certain the design is correct before fabrication. Fabri-

cation itself will take several weeks and several thousand dollars. Changing a software design, on the other hand, is as easy as altering data within the computer's memory - although, in many cases test examples will also be run before the altered software is 'released' to outside users.

6. ASIC's are outside your control. With a catalogue part system the development engineer has all the parts he needs in store before he starts. If he is unsure about how a subsystem will behave he can breadboard it and see what happens. 'Suck it and See' is preferable to formal verification for the average systems engineer. There are sound reasons for this preference: you get results faster and the results are more meaningful. Building a system and watching it work gives much more confidence than looking at simulation results on a computer. When an ASIC is to be used as a subcomponent in a larger system the problems are worse because it may be impossible to get a good simulation model of the behaviour of the surrounding system.

The problems discussed above all stem from three basic properties of ASIC technology:

- 1. The customisation of ASIC's is static and involves expensive processing.

- 2. The structure of ASIC's is irregular and problem specific.

- 3. ASIC's have a small range of application.

It is important to note, however, that at the present state of VLSI technology none of the above problems are insuperable with proper CAD tools and ASIC technology has allowed the development of many extremely complex new products. The question is whether ASIC technology can continue to provide access to the considerable potential benefits of VLSI as device sizes continue to get smaller and we move towards Wafer Scale Integrated systems or whether a new design style will be required.

# 1.3 Configurable Hardware.

In this section we will consider a third paradigm for computation: configurable hardware. In this system the interconnection of active logical elements is determined by a control store. This potentially provides much of the performance of dedicated hardware with some of the flexibility of software.

- 1. Instruction Fetch/Decode. In a configurable hardware system the 'instruction' word which determines the interconnection of logic elements is normally loaded before the computation starts and remains constant throughout the computation. Thus, in most cases, there is no instruction fetch overhead during the computation phase.

- 2. Word Length / Calculation Efficiency. Like conventional hardware configurable hardware can use units tailored exactly to the computation required.

- 3. Pipelining. Configurable hardware systems can take advantage of pipelining and other parallelism available in the algorithm at the bit level often resulting in very large performance gains over conventional computers.

- 4. Reusable. Unlike traditional hardware configurable hardware can be reconfigured an unlimited number of times to compute different functions. This flexibility is not as great as that of software since the functions which can be computed will be heavily constrained by the amount of configurable hardware available and the input/output connections to it which are both fixed for a given system. The additional flexibility will, however, make it economic to provide relatively large amounts of configurable hardware within a computer system since the cost can be spread over many different applications.

Naturally, the 'hybrid' configurable hardware technology has also many disadvantages.

- Speed. Configurable Hardware will always be considerably slower than conventional hardware because of delays introduced by the switching system.

Often this drawback can be reduced since it will be economic to use better processing technology in the re-usable configurable system. Increased area can usually be traded for speed, for example, by providing extra parallelism.

- 2. Area. The overhead of the control store and switching circuits means that a large increase in area over conventional hardware is unavoidable. This overhead will be especially large in memories which are normally implemented as array structures designed at the mask level.

- 3. Flexibility. Configurable Hardware cannot approach the flexibility of conventional processors for complex computations. In general, it is most suitable for simple 'inner-loop' computations with high repitition counts which could be considered for implementation in conventional hardware.

Because of these drawbacks Configurable Hardware is not seen as a replacement for either conventional software or hardware but as an alternative system which could potentially implement some important applications more efficiently than either of the previous techniques. Three particular target application areas have been identified: any one of these would, in itself, justify the development of the Configurable Logic system.

## 1.3.1 EPLD Replacement.

At the moment there is a very large market for Electrically Programmable Logic Devices (EPLD's) in board level systems. These devices can simplify design, reduce package count (by replacing several small TTL devices) and provide extra flexibility by allowing changes in circuits to be made without changing Printed Circuit Board (PCB) layouts. As time progresses the fraction of systems implemented using programmable devices is increasing.

At present, this market is dominated by two-level AND/OR Programmable Logic Array (PLA) devices although some more general gate-array like architec-

| n | Num. Inputs | Num. Outputs | Single PLA | Many PLA's |

|---|-------------|--------------|------------|------------|

| 1 | 2           | 2            | 3          | 3          |

| 2 | 4           | 3            | 11         | 6          |

| 3 | 6           | 4            | 37         | 9          |

| 4 | 8           | 5            | 75         | 12         |

Table 1-1: Number of Product Terms vs Number of Inputs in Adder.

tures are emerging [Xilinx86]. Two level architectures are fundamentally inappropriate for implementing complex systems: as device densities increase all that you can do is increase the number of inputs, outputs and product terms available. Table 1-1 shows how the number of product terms (after minimisation) increases with the number of inputs in an adder when it is implemented as a chain of one bit adders and as a single n bit adder: clearly simply increasing the size of a single array is not a practical way of building large adders. Instead, the function must be partitioned into many different functional blocks: often designed using different techniques. This requires a more general programmable structure.

# 1.3.2 Prototype System for ASIC's.

Systems designed using the configurable architecture developed in this thesis can also be mapped efficiently to both semi-custom and full-custom silicon implementations. The dynamically programmable technology provides an ideal breadboarding system for designs which will eventually be implemented in silicon, allowing prototype designs to be tried out within the target system (although clock rates may have to be reduced). Directly implementing the function using dynamically programmed devices provides logic simulation at speeds which even the most expensive hardware accelerators cannot approach at relatively low cost.

## 1.3.3 Algorithm Machine.

This application is more of an exciting possibility than a proven capability. It will be shown (in Chapter 5) that a huge array of configurable cells can be built using wafer scale integration. Eight wafers of configurable chips designed using  $1\mu m$  rules would give a  $1 \text{M} (2^{20})$  cell array. The question of 'virtualising' such arrays to provide many potentially very large 'logical' arrays from a single physical array will be addressed in Chapter 8. What can be done with this amount of logic? Hopefully, systolic algorithms for applications like sorting, priority queues, searching and signal processing can be mapped onto the cells. This seems to make much more sense than having different special purpose processors for each application where hardware acceleration is required.

#### 1.4 Overview of Thesis.

- 1. Chapter One. This chapter has covered the basic ideas behind configurable hardware and suggested target applications for the configurable architecture to be developed in the rest of this thesis.

- 2. Chapter Two. This chapter takes a 'high level' look at the resources available to implement configurable hardware and the different ways in which they can be utilised. Metrics are developed for measuring the efficiency of architectures and the limitations of the current two-level logic EPLD's are examined in detail. The effect on utilisation of increasing the generality of the basic cells in Programmable Logic Arrays is examined to motivate the search for more flexible architectures. Finally, a discussion of timing disciplines for use in programmable systems is presented.

- 3. Chapter Three. This chapter concentrates on the design of flexible configurable systems. A mapping of the design space is set out and new cellular architecture called Configurable Array Logic (CAL) is proposed. This map-

ping of the design space is then used to compare the present design with several important earlier designs.

- 4. Chapter Four. This chapter deals with the VLSI implementation of the cellular architecture presented in Chapter 3. The design of the control store and switching struture are developed in detail with several possible implementations being considered. Design and performance figures for leaf cells designed to implement CAL are given as well as possible improvements to the design. The way in which the design will scale with improving technology is discussed.

- 5. Chapter Five. This chapter will discuss specific implementations of the configurable logic architecture in VLSI. Firstly, a chip implemented using the leaf cell layouts of Chapter 4 is presented and the methods adopted to verify the design and algorithms to test fabricated chips are discussed. Secondly, a statically programmed version in which the cellular array is configured by the second metal mask (the CLA) is dealt with. Thirdly, a proposed extension of the VLSI implementation of CAL described in Chapter 4 to Wafer Scale Integration is covered.

- 6. Chapter Six. This chapter deals with CAD tools for the Configurable Logic system: the CAD system required to convert conventional high level language programs into configurable logic designs is mapped out and potential problems discussed. The purpose of this chapter is to show that algorithms developed for silicon compiler systems can readily be adapted for cellular systems and that it should be practical to integrate support for configurable logic into an existing silicon compiler environment. CAD tools developed during the course of the project to support the design examples in chapter 7 are also covered. Two major tools are treated in detail: a logic synthesis program and a channel router.

- 7. Chapter Seven. This chapter covers examples of the application of the configurable logic technology. Four examples are covered: a digital stopwatch

chip, a Data Encryption Standard (DES) [NBS77] encryptor, a unit to compute the 3-4 distance transform (which occurs in image pattern matching) and a design sketch for a system to implement cellular-automata models used in fluid-flow simulations. The first example is typical of the sort of application in which CAL could be used as an EPLD replacement and has been implemented using several different technologies. Area comparisons are given to show where configurable logic fits into the design space. The second example is a much larger system which requires many CAL chips built into a larger array at board level. This example illustrates the applicability of CAL to the prototyping of ASIC's or as an accelerator for conventional computers. The third example is intended to illustrate the use of configurable logic to accelerate 'inner-loop' computations in conventional algorithms. The fourth example illustrates how configurable logic can be used to implement a particular cellular-automata model: cellular-automata are becoming increasingly accepted by the physics community as models for a wide range of phenomena.

8. Chapter Eight. This chapter draws together the research presented in the preceding chapters and sets out possible directions for further research. A design for a 'virtualised' configurable logic system is outlined.

# Chapter 2

# Principles of Configurable Systems.

This chapter develops a gate level model of configurable systems. Based on this model some fundamental measures of the efficiency of configurable systems are presented.

We then turn our attention to the central design goal of our architecture: the efficient realisation of ASIC size systems and the implications of the generality of this goal on implementations are examined.

The chapter concludes with a discussion of timing disciplines for such programmable systems. This is an area which has received almost no attention in the past.

### 2.1 Circuit Model.

At this point it is advantageous to have a more formal model of circuits. This will allow fundamental bounds on the cost of implementation to be found. The question of at what level to model the circuit is a difficult one. There are two main options: gate level and switch (transistor) level. The second option is nearer the implementation and reflects the fact that the configuration circuitry and the logic circuitry are both made up of switches. It has, however, some important disadvantages.

- Convenience. Most systems engineers prefer to design using logic gates rather than switches and all configurable systems to date operate at this level of abstraction. This has the consequence that the functions realised are over {0,1} instead of {0,1, Z}. At this level of abstraction wires have a direction and a single source.

- 2. Directions of Signal Flow. When designing configurable systems it is important to take account of the fact that the transistors which implement the switches are far from being ideal components. It is reasonable to impose an additional rule that no path may go through more than a small number of switches without buffering to restore logic levels. The introduction of buffering forces a direction on wires, this can be ignored in a gate level abstraction but the buffers would need to be explicitly modelled at the switch level.

- 3. Implementation Tricks. As we will see in Chapters 3 and 4 there are many important low-level techniques which can be used to increase the efficiency of implementations. At first glance it would seem that switch level models would be a better choice to describe such circuit structures. This is not the case since they often rely on additional properties of physical implementations such as resistance and capacitance and require analogue rather than digital techniques to model properly. Simple equivalent gate level circuits can be found and it is much easier to develop a clean and self-consistent gate level model of general hardware than it is to develop a switch level one.

#### 2.1.1 Definition of Circuit.

We are considering a circuit as being an interconnection of gates, without loss of generality we can assume that all the gates have two inputs and one output. These gates implement a function g chosen from a basis set  $\Omega = \{g : \{0,1\}^2 \to \{0,1\}\}$ .

A c gate circuit C can be modelled as a graph C = (G, W) where the gate set G is an enumerated set of two input gates (vertices) and the wire set W is a set

of connections (edges). The gate functions g are chosen from the basis set  $\Omega$  so  $G = \{(i, g_i) : g_i \in \Omega, 0 \le i < c\}.$

The wire set W is more complicated: each member of this set is a tuple (source, sink) representing a connection between gate outputs (or circuit inputs) and a gate input or circuit output. A source may take part in several such tuples (since a gate output will often drive several gate inputs) but a sink may take part in at most one tuple (since connecting several sources together is not allowed in a gate level model). We can, therefore, specify the wire set W by enumerating the sources for every gate input. If we label each gate using the integers from 1 to c then we can label all possible sources by using  $1 \dots c$  to represent the output of the corresponding gate. Similarly the sinks can be labelled using integers from  $1 \dots 2c + 1$  (since there are two inputs per gate). Thus  $W = \{(i,j) : 0 \le i \le c, 1 \le j < 2c\}$ , where no two members of W have the same sink j. Unconnected sinks or sinks which are circuit inputs have no corresponding entry in W. An alternative way to model the wire set W would be as an array containing the sources for each sink with a special nil value for unconnected sinks.

There are several points worth making about this model of circuits.

- 1. Inputs and Outputs. This model does not represent circuit inputs and outputs in any way: circuits are treated as interconnections of gates. Some gate inputs and outputs may be unconnected. The reason for not treating inputs and outputs explicitly is to provide a notion of c gate circuit: if the n inputs and m outputs were modelled then we would need to think about (c,n,m) circuits and the size of the circuit could be increased arbitrarily just by adding more feed through connections between inputs and outputs. A model which dealt with inputs and outputs explicitly might allow a more complete analysis but would complicate the mathematics. Note that we do not require the graph to be connected, i.e. a circuit can be composed of several unrelated subcircuits.

- 2. Wire Model. The definition of edge nodes prevents gate outputs being con-

nected together. A single wire in the physical circuit connecting a gate output to many gate inputs is modelled by many edges in the graph.

3. Two Input Gates. In physical circuits gates with a fairly arbitrary number of inputs are possible, however the area of the gate increases linearly with the number of inputs. An s input gate can always be replaced by a network of 2 input gates so there is a reasonable algorithm for converting physical circuits into our model. Counting two input gates is a better cost metric than counting gates with arbitrary numbers of inputs since it directly reflects the area required.

Equivalence of Circuits. In simple terms two circuits are equivalent if the same gate functions are connected in the same pattern. Specifying this formally is complicated by the fact that the labellings of gates used in the circuits may well be different: for example a NAND gate labelled 3 in one circuit may be labelled 16 in the other and a wire from the output of that gate could be (3,25) in the first circuit and (16,30) in the second. If the two circuits are equivalent then if we replace all the 16's if the second circuit with 3's and so on for the other gate numbers then we will end up with two identically labelled graphs. This will not happen if the two circuits are not equivalent - for example if there was an extra connection from the NAND gate in the second circuit.

More formally, two circuits  $C_1 = (G_1, W_1)$  and  $C_2 = (G_2, W_2)$  are equivalent if and only if there exists a one to one and onto mapping  $\mu$  between gate labels in  $C_1$  and gate labels in  $C_2$  such that  $G_1 = G_2$  and  $W_1 = W_2$  where  $G_2 = \{(\mu(i), g_i)\}$  and  $W_2 = \{(\mu(i), \mu(jdiv2) + (jmod2))\}$ .

Containment of Circuits. A circuit is contained within another circuit if it is equivalent to part of the second circuit. More formally, circuit  $C_2$  is contained in circuit  $C_1$  if and only if there is a one to one (but not necessarily onto) mapping between labels in  $C_2$  and labels in  $C_1$  such that  $G_2 \subseteq G_1$  and  $W_2 \subseteq W_1$  where  $G_2 = \{(\mu(i), g_i)\}$  and  $W_2 = \{(\mu(i), \mu(jdiv2) + (jmod2))\}$ .

Subtraction of Circuits. Based on the idea of containment above we can define what it means to subtract a subcircuit from a larger circuit, informally we delete all the gates and wires corresponding to the subtracted circuit. If  $C_2$  is contained in  $C_1$  then  $C_1 - C_2 = (G_1 - G'_2, W_1 - W'_2)$  where  $G'_2 = \{\mu(i), g_i\}$  and  $W'_2 = \{(\mu(i), \mu(jdiv2) + (jmod2))\}$ .

Composition of Circuits. A circuit C is composed of circuits  $C_1, C_2, C_3, \ldots, C_n$  if and only if  $((((C - C_1) - C_2) - C_3) - \ldots - C_n) = (\emptyset, \emptyset)$ .

### 2.1.2 Definition of Configurable Circuit.

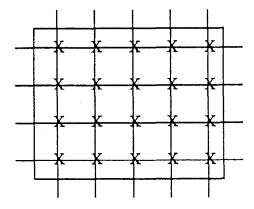

A configurable circuit PC is modelled as the quadruple (G,S,W,V) where G is a set of gates as above S is an enumerated set of selectors (or multiplexors)  $s_r(x_0,\ldots,x_n,i)=x_i, 0 \leq i < n, n=2^r,W$  is a set of wires as above except that selectors can now be used as sources or sinks and V is a control vector which selects the sources chosen by the selectors. Every bit of V is connected to exactly one selector control input.

Definition of Emulation. A configurable circuit PC with control vector V emulates a circuit C if when all the selectors in PC are removed and all edges in PC with a selector as source are replaced by edges with the selected input as source then the circuit C is contained in the resulting circuit. Note that the circuits do not have to be equivalent because not all the resources in PC need be used.

#### 2.1.3 Definition of c-CLM.

A c gate Configurable Logic Module c-CLM is a programmable circuit which, according to a control vector V will emulate any c gate circuit as defined above.

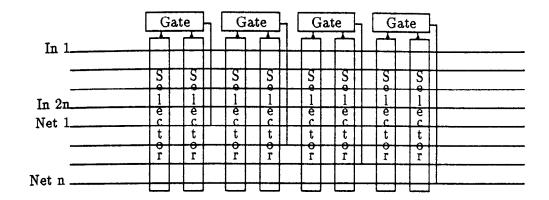

Figure 2-1: Architecture which meets lower bound.

#### 2.1.4 Lower Bounds.

Gates. Obviously, a c-CLM must contain at least c gates.

Inputs and Outputs. A c-CLM must contain at least 2c inputs and c outputs (consider a circuit where every gate computed a function of two different input variables).

Memory. If we count the number of c gate circuits then we can easily determine the minimum amount of memory needed to control a c-CLM.

From the definition of circuit it follows that each sink is connected to at most one source: there are 2c + 1 possible sinks (2c gate inputs or unconnected) and c + 1 possible sources (c gate outputs or unconnected) so there are  $(2c + 1)^{c+1}$  possible interconnections. We must also consider the number of possible functions which each gate can perform  $|\Omega|$ , giving a total number of circuits  $|\Omega|(2c + 1)^{c+1}$ .

This implies that at least

$$\lg(|\Omega|(2c+1)^{c+1}) = \lg(|\Omega|) + (c+1)(\lg(2c+1)) = O(c\lg(c))$$

bits of RAM will be required to control a c-CLM.

Surprisingly, perhaps, there is an architecture which obtains this lower bound (Figure 2-1). This architecture is not practically interesting for circuits with large numbers of gates since it requires global wiring for each net.

#### 2.1.5 Circuits and Functions.

The function performed by a circuit can be represented as  $f: \{0,1\}^n \to \{0,1\}^m$ , where n is the number of inputs and m is the number of outputs. In order to decide what function a circuit computes one must identify input and output terminals on the circuit. There are now 2c + m + 1 (unconnected outputs are still possible) sinks and c+n+1 possible sources giving  $|\Omega|(2c+m+1)^{c+n+1}$  possibilities. Many of these possibilities may compute the same function. Determining whether two distinct circuits compute the same function is a difficult problem.

It may seem more natural to count distinct functions rather than distinct circuits but there are good reasons for our choice.

- 1. Different Realisations are Useful. In a general configurable device it is desirable to be able to implement the same function in several different ways: for example there are many possible implementations of the addition function and designers will want to select one with appropriate delay and area for their system. This is to be contrasted with previous architectures where the configurable system was intended to implement one block of random logic: here multiple realisations of a given function would be considered an efficiency overhead.

- 2. Number of Boolean Functions. There are 2<sup>2<sup>n</sup></sup> combinational functions f: {0,1}<sup>n</sup> → {0,1} and (2<sup>m</sup>)<sup>2<sup>n</sup></sup> functions f: {0,1}<sup>n</sup> → {0,1}<sup>m</sup>. The explosive growth in the number of functions means that almost all n input combinational functions require O(2<sup>n</sup>) gates to implement [Savage76,Shannon49]. This implies that defining CLM's in terms of computing all functions of n variables would place circuits of very different complexity in the same cat-

egory. Counting gates gives a much better indication of device size than counting input variables.

3. Sequential Circuits. The general interconnection of gates permitted by our circuit model allows latches to be built, therefore some of the circuit permutations correspond to sequential rather than combinational logic. This makes counting functions impossible (since such a circuit could emulate a Turing machine with sequential logic providing the 'tape').

## 2.2 Efficiency.

The most important measure of the cost of a one bit wide configurable circuit is the number of bits of control store. There are two important reasons for this: firstly the control store is likely to account for a high percentage of the total area and secondly the size of the data-path will normally scale almost exactly with the number of bits of control store. This is because the width of the control vector means that there is no possibility of implementing the two separately with interconnecting wires: they must be intermingled in the same structure so that each bit of control store is situated close to the switches it controls.

# 2.2.1 Efficiency of Configurable Circuits.

We wish to define efficiency in terms of the 'value' we get from each bit of the control store: for maximum efficiency we would expect each permutation of the control vector V to result in a different circuit being emulated. We can formalise the idea of different circuits as follows.

**Definition of Distinct.** Two permutations of a configurable circuit with control vectors  $V_1$  and  $V_2$  are distinct if and only if the two emulated circuits  $C_1$  and  $C_2$  are not equivalent.

Figure 2-2: Wasted Signals.

Thus, we define the efficiency E of a configurable circuit which realises n distinct circuits with a control vector of length |V| as

$$E = \frac{\lg(n)}{|V|}.$$

This gives E=1 when every permutation of V has a corresponding distinct realisable circuit.

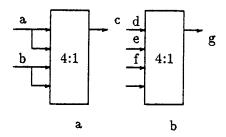

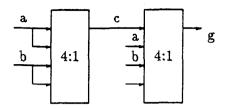

The purpose of this metric is to detect wasted control signals, figure 2-2 shows examples of wasted signals. In figure 2-2a control signals are wasted by having the same data signal on more than one input of a multiplexor: a 2:1 multiplexor with only 1 control line could realise as many distinct configurations. In figure 2-2b one of the permutations is wasted by having an unconnected input to the multiplexor.

This definition of efficiency is intuitive but to make it useful for comparing different configurable logic designs some method of computing it efficiently must be available. The obvious method of generating all possible control signal permutations and comparing the resulting circuits with each other is totally impractical for larger circuits. We need some method of taking advantage of the regularity present in actual designs to reduce the amount of computation. We would also like an efficiency figure for an architecture rather than an efficiency for a particular fixed size circuit.

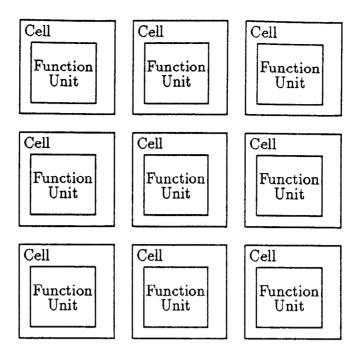

Let us consider programmable circuit PC as being composed of identical programmable subcircuits or 'cells'  $pc_0, \ldots, pc_{n-1}$ . Let  $n(pc_i)$  be the number of circuits

Figure 2-3: Composition Can Reduce Efficiency.

emulated by pc; then the efficiency of PC is

$$E(PC) \leq \frac{\sum \lg(n(pc_i))}{\sum |V_i|}.$$

Discussion. Consider the number of control signals to PC,  $\sum_{i=0}^{n-1} |V_i|$  (if control signals were shared between  $pc_i$  and  $pc_j$  then we would consider them to be a single subcircuit). It remains to show that the number of circuits is not increased by any fixed composition. When the number of circuits was calculated for the subcircuits  $pc_1, \ldots, pc_n$  then the input terminals were unknown and assumed to be on different nets. Here, some of them will be on known nets possibly the same as other terminals of the subcircuit: therefore the efficiency could be smaller but since there are no more unknowns it cannot be larger. Figure 2-3 shows an example of a circuit whose efficiency is less than that of its subcircuits.

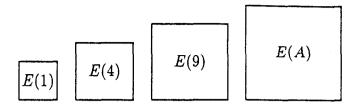

Architectural Efficiency. The efficiency of a regular array architecture E(A) can be defined as the limit of array efficiency as the array size tends to infinity (figure 2-4). Thus

$$E(1) \ge E(4) \ge E(9) \ge \ldots \ge E(A).$$

Cell Efficiency. In many of the practical architectures we will be concerned with the programmable structure is composed of an array of identical cells. In this case the efficiency of the basic cell E(1) in figure 2-4 is a very important parameter since it is relatively easy to calculate and is a reasonable predictor of architectural efficiency.

Figure 2-4: Architectural Efficiency.

### 2.2.2 Functional Efficiency.

Many programmable logic architectures have been designed to implement irregular combinational functions such as those found in control stores. For such architectures it is more appropriate to measure efficiency in terms of the number of distinct functions realisable f as

$$E = \frac{\lg(f)}{|V|}.$$

These architectures usually have limited connection patterns and choices of gate types so counting the number of functions implemented is sometimes feasible.

## 2.2.3 Utilisation.

As well as having a measure of how efficient a programmable architecture is in its utilisation of control store it is tempting to measure the overhead in implementing a particular circuit on a certain programmable structure. This sort of figure is very easy to obtain since one just needs to add up all the resources used and divide by the resources provided. Utilisation figures can be very misleading since bad designs which use unnecessary resources make the programmable architecture look better by increasing utilisation. Similarly, poor designs of programmable architectures will often force roundabout wiring paths (using more selectors) and have a higher utilisation than good designs. For these reasons utilisation figures must be treated with care. One important utilisation statistic is the cell utilisation which is the ratio of cells used in a particular function to cells provided.

AND Plane.

OR Plane.

Figure 2-5: FPLA Cell Designs.

# 2.3 Design Goals.

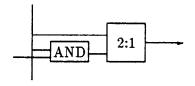

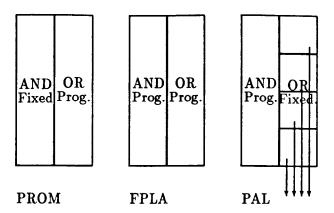

Before we go any further it is important to have a clear idea of what range of application we want our configurable system to have. The central design aim is to produce a configurable system which can emulate any system realisable using an ASIC with only a 'small' increase in area and reduction in speed. Let us consider exactly what this entails: the functionality of the ASIC can be described as a function  $f:\{0,1\}^n \to \{0,1\}^m$ . This immediately suggests an implementation: any boolean function can be implemented using a Programmable Logic Array (PLA) and there is a dynamically configurable equivalent technology the Field Programmable Logic Array (FPLA). We will consider FPLA's to be composed of an array of two kinds of small flexible cell illustrated in figure 2–5. The first kind makes up the AND plane and the second the OR plane. This is a fairly good model for RAM based programmable PLA's but is significantly different from the normal fuse based FPLA's where wires are undirected and very high fan in gates are available.

One important property of nearly all ASIC designs is that they are composed of many functional blocks. Assume there are s blocks, each of these also realises a function

$$g_i: \{0,1\}^{n_i} \to \{0,1\}^{m_i}, 0 \le i < s.$$

Each of these functional blocks may in turn be composed of other functional blocks and the ASIC function f is a hierarchical composition of these subfunctions.

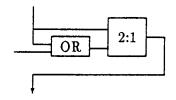

Let us consider the implications of this for an FPLA implementation. Define the area function A(f) of an FPLA implementation of f to be the number of cells used, this gives A(f) = p(f)(n+m) where p(f) is the number of product terms (because the FPLA is a rectangular array (n+m) cells wide and p(f) cells high). Let us assume that the subfunctions  $g_i$  are disjoint (i.e. share no inputs or outputs). The area for separate implementation is

$$\sum_{i=0}^{s-1} ((n_{g_i} + m_{g_i})p(g_i))$$

whereas the area for a single logic block is

$$A(f) = (\sum_{i=0}^{s-1} (n_{g_i} + m_{g_i})) (\sum_{i=0}^{s-1} p(g_i))$$

This is illustrated in figure 2-6. To simplify the analysis let us assume the subfunctions are the same size so  $n_{g_i} + m_{g_i} = a$  and  $p(g_i) = b$  for all  $g_i$ ,  $0 \le i < s$ . Then the area of a separate implementation over the area of a composite implementation is

$$\frac{\sum A(g_i)}{A(f)} = \frac{s(ab)}{(sa)(sb)} = \frac{1}{s}$$

Thus the area of a separate implementation increases linearly with the number of functions s whereas the area of a composite implementation increases as  $s^2$  [Wood79]. It should be noted that this is an average case analysis: it is easy to find values which are better or worse.

Obviously, the analysis is incomplete: several other important factors must be considered.

1. Overhead Circuitry. Each PLA will have some associated overhead circuits at the edges: the costs for this scale better with the single array implementation.

Figure 2-6: Area of Disjoint Functions Implemented in Single Array.

- 2. Functions are not completely disjoint. In an actual ASIC the functions implemented by separate subunits will not be completely disjoint: they may use outputs from other subunits as inputs or share inputs with other subunits. Subfunctions can themselves be decomposed hierarchically.

- 3. Logic Minimization. Logic minimization algorithms have large computational complexity and much better results can be obtained for small subunits than for a single large logic block.

- 4. Concurrency. Decomposing the function into many logic blocks provides the potential for concurrent operation of blocks and pipelining between them. The delay through a small block is likely to be lower than the delay through a large one after some critical size is exceeded.

These considerations imply that if we wish to build ASIC size systems it is essential to be able to implement subfunctions using separate blocks. This has important consequences for the structure of such a device.

#### 2.3.1 Device Structure.

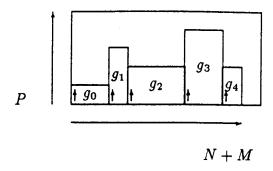

We have seen that in order to build a reconfigurable chip capable of efficiently implementing whole systems several logic blocks will have to be available on the chip. Some means of connecting these together to form the complete function will be required. We have a set of s subfunctions  $g_i, 0 \le i < s$  where s is unknown,  $p(g_i)$ is unknown  $m_i$  is unknown and  $n_i$  is unknown. In the most general case we cannot say that  $n_i \leq n$  and  $m_i \leq m$  since the subfunctions will not be totally disjoint: it is very common to find subunits in an ASIC with more inputs and outputs than the chip itself. A first attempt at a solution would be to fix a maximum value of s,S and put S identical logic blocks with fixed numbers of inputs,outputs and product terms N,M and P on a chip with some interconnection structure between them. If we split our function f into subfunctions which do not exceed any of these limits then all is well although a potentially large amount of space will be wasted by choosing worst case values of N, M, P (figure 2-7). We can calculate the expected utilisation of each subunit for the case  $P = 2^N$ : if we wish to ensure that all N input functions can be realised then this is the decision we would have to take. FPLA's with all 2<sup>N</sup> product terms provided are known as PROM's.

Utilisation of PROM. The average number of cells required in a PROM is

$$\frac{(\sum_{n=1}^{N}(\sum_{m=1}^{M}(n+m)2^{n}))}{MN} = \frac{2^{N}(M+2N-1)-M+1}{N}$$

(because there are MN possible sizes of PROM which fit into a  $2^N \times (M+N)$  array with  $2^N(M+N)$  cells) giving an average utilisation of

$$U = \frac{2^N(M+2N-1)-M+1}{N(N+M)2^N} = \frac{1}{N} + \frac{N-1}{N(N+M)} - \frac{M-1}{N2^N(N+M)} \simeq \frac{1}{N} + \frac{1}{N+M}.$$

This assumes that subfunctions with n inputs require  $2^n$  product terms i.e. they are implemented using smaller PROMS. We can see that as N gets large on average only about  $\frac{1}{N}$  of the PROM will be used: even this is a considerable overestimate because most n input subfunctions will require much less that  $2^n$  product terms. The conclusion is obvious: large PROMS should be avoided at all costs. This suggests that we examine the consequences of having subfunctions which overflow fixed size subunits.

Consequences of Overflow. Suppose that one of the subfunctions  $g_i$  does not fit - there are several ways in which this could happen.

- 1. Not Enough Outputs. This situation can be solved by using more than one array and duplicating the inputs and product terms. This imposes a considerable overhead.

- 2. Not Enough Inputs. Suppose there were t inputs too many. Then the problem can be solved using a t+1 input decoder and  $2^{t+1}$  subunits. The decoder could be implemented using another subunit but for even moderate size t there is a good chance of requiring too many outputs (since the number of outputs grows as  $2^t$ ). The overhead here is the decoder and the extra wiring.

- 3. Not Enough Product Terms. This is the most likely situation. Many functions have large numbers of inputs and outputs but in the worst case 2<sup>n</sup> product terms will be required. This situation can be worked round by using two arrays duplicating the inputs and OR'ing the outputs. The overhead here is in the wiring necessary to move inputs and sub-outputs around the chip.

- 4. Not enough Subunits. In this case multiple subfunctions can be combined into a single array. This has the overhead discussed in the last section.

We can see, therefore, that the provision of many smaller fixed sized PLA units to implement subfunctions does not provide the required efficiency to implement large ASIC sized systems of a programmable structure.

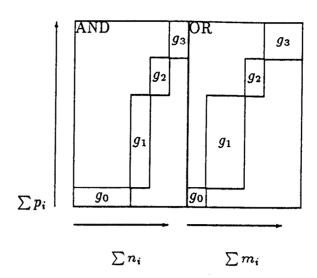

# 2.3.2 Utilisation and Cell Generality.

In this section we will investigate the effect of increasing the generality of the basic cell on the utilisation of the array.

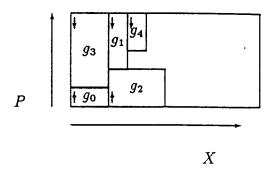

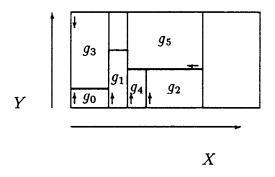

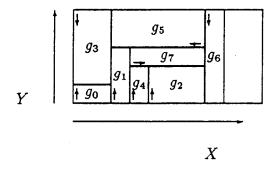

Row Folding. Suppose you had a single cell that could either form part of an AND plane or part of an OR plane. If you built your S subunits from these cells

Figure 2-7: Stage 0.

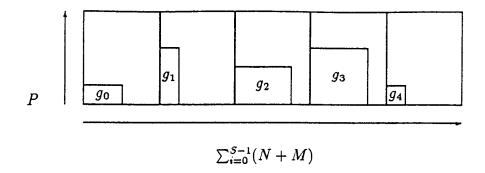

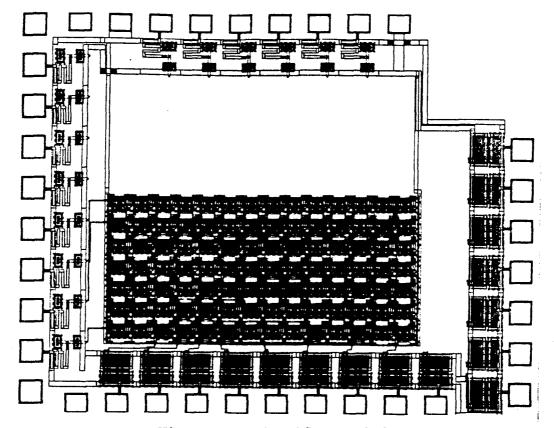

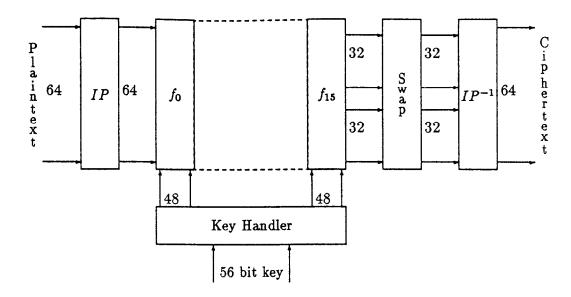

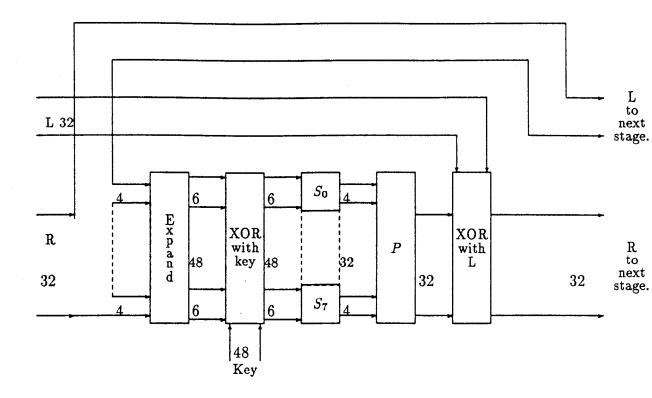

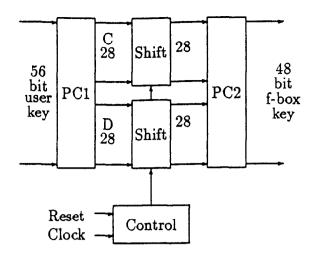

you would no longer have to fix N and M but only N+M. Suppose further that all S subunits were abutting each other. With such flexible cells the point at which one array ended and another started would no longer need to be fixed. We would not have to fix N,M and P for each g but only  $\sum_{i=0}^{S-1} (N+M)$  and p (figure 2-8).